# **NVMM Cache design: Logging vs. Paging**

Work in progress paper: A comparison between two caching mechanisms

**Rémi Dulong<sup>1,2</sup>**, Quentin Acher<sup>3</sup>, Baptiste Lepers<sup>1</sup>, Valerio Schiavoni<sup>1</sup>, Pascal Felber<sup>1</sup>, Gaël Thomas<sup>2</sup>

<sup>1</sup>University of Neuchâtel, Switzerland <sup>2</sup>Télécom SudParis, Evry, France <sup>3</sup>ENS Rennes, France

#### Context

Modern NVMM is closing the gap between DRAM and persistent storage, both in terms of performance and features. Having both byte addressability and persistence on the same device gives NVMM an unprecedented set of features, leading to the following question: How should we design an NVMM-based caching system to fully exploit its potential?

We built and compared two caching mechanisms, *NVPages* and *NVLog*, based on two radically different design approaches.

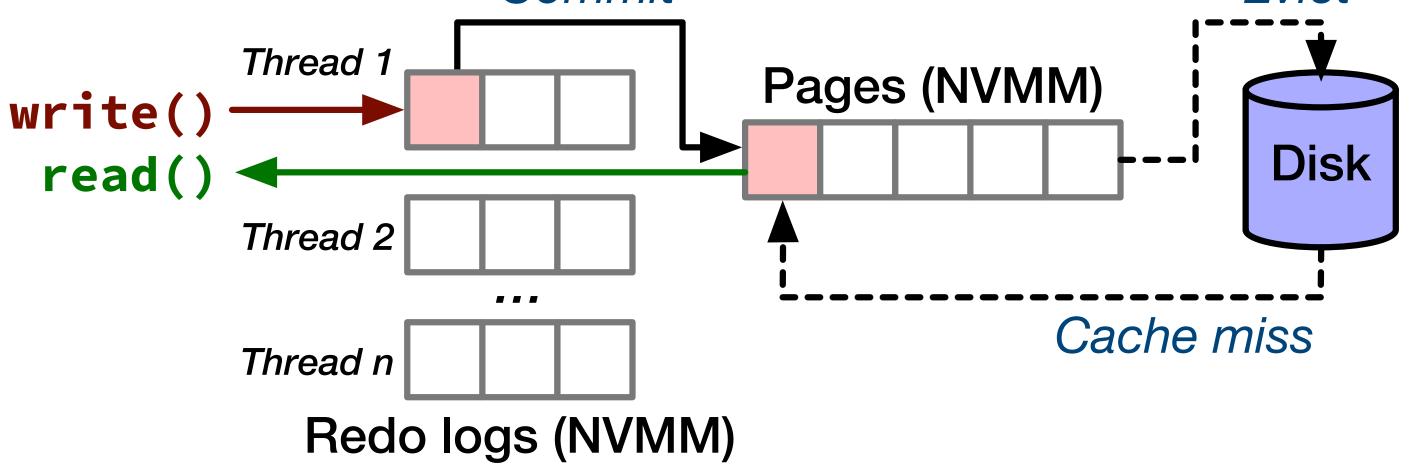

#### **Design:**

- One page cache in NVMM, used for reads and writes

- One redo-log per thread

- Inspired from the *Linux Page Cache*

### **Pros**:

- Provides several GiB of non-volatile pages

- No DRAM footprint

- Simple design  $\bullet$

#### Cons:

Does not benefit from DRAM bandwidth

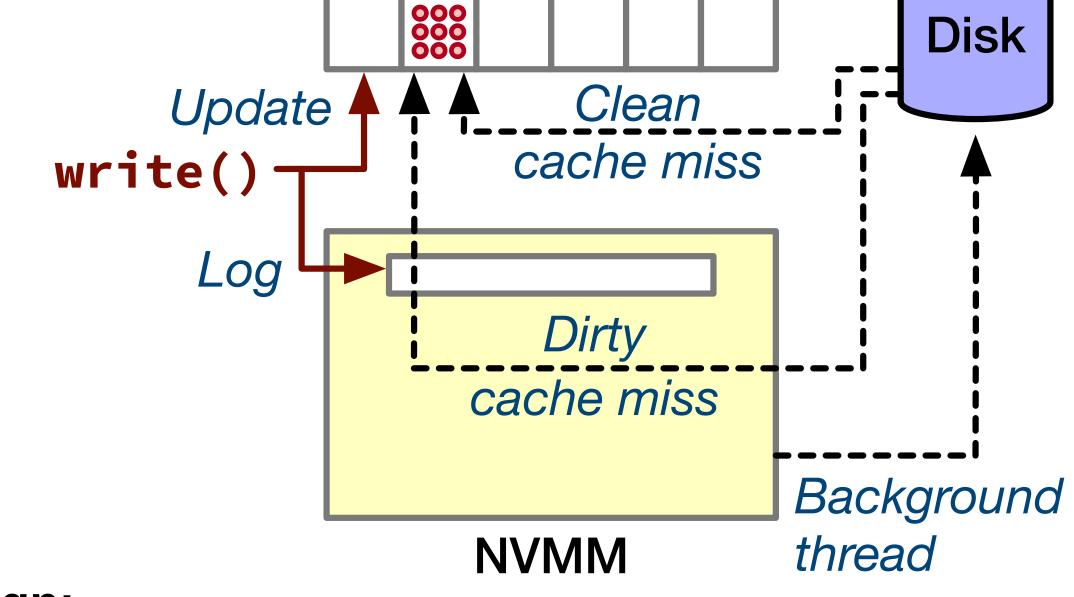

#### **Design:**

- NVMM is used as a Log of pending writes

- A background thread writes changes to disk

- A small DRAM page cache keeps hot pages updated

### **Pros**:

- Writes in NVMM, reads in DRAM

- Small DRAM footprint (a few GiB)

**NVMM Caches**

#### Cons:

Complex design (*Dirty cache miss*, synchronization...)  $\bullet$

# **Evaluation**

(s)

100

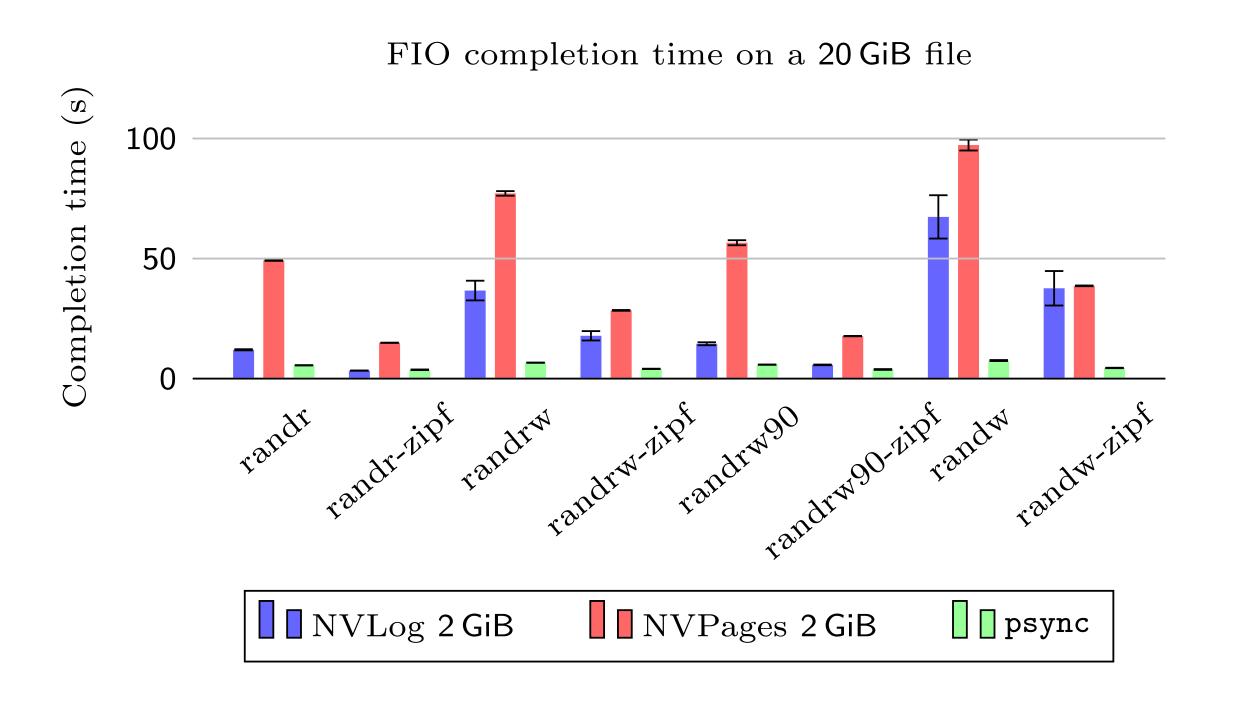

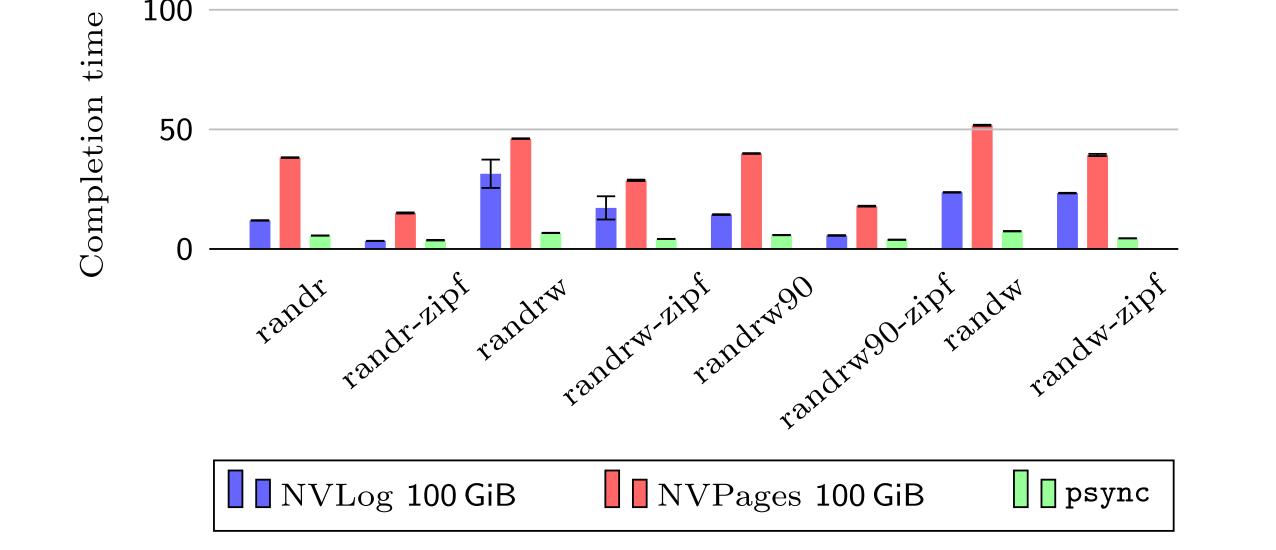

#### FIO completion time on a 20 GiB file

## Why should we consider NVMM caches?

- High persistence guarantees & Crash resilience

- Compatibility with legacy file systems

- Does not limit storage capacity to NVMM capacity

- **Simpler** than a hybrid file system

# What should a NVMM cache provide?

- A transparent POSIX-like interface

- High capacity with NVMM **bandwidth** & **latencies**

#### Conclusion

In its current state, **NVLog** seems to have a

**Baseline:** The "psync" IO engine of FIO uses regular pread and pwrite operations, with no guarantee of persistence.

clear edge over **NVPages**. It performed better on all workloads, even on those we expected NVPages to be more efficient. That said, some additional logic should be added to both caches implementations in order to evaluate their performance on multithread workloads.

**Unine**<sup>•</sup> Université de Neuchâtel

remi.dulong@unine.ch

NVMW23, Non-Volatile Memory Workshop 2023 - University of California, San Diego