# Circadian Rhythm: A Candidate for Achieving Everlasting Flash Memories

\*M. Ceylan Morgul, ^Xinfei Guo and \*Mircea Stan

\*University of Virginia, Charlottesville, VA, USA

^University of Michigan – Shanghai Jiao Tong University Joint Institute, Shanghai, China

{ceylan, mircea}@virginia.edu; xinfei.guo@sjtu.edu.cn

This work was supported in part by Semiconductor Research Corporation (SRC) under

the Center for Research on Intelligent Storage and Processing in-memory (CRISP)

# Reliability of FLASH

- Flash memories: dense, non-volatile, low latency, random access I/O

- Endurance limitation: wear-out by using (Program/Erase cycling)

- Reliability and Sustainability are important now more than ever

Solutio

| SLC: 30-160 us   | SLC: 100k P/E             | QLC: 4 & 16                   |

|------------------|---------------------------|-------------------------------|

| QLC: 140-3102 us | QLC: 1k P/E               | SLC: 1 & 2                    |

| Low Latency      | Endurance (Program/Erase) | Density (bits/cell & state #) |

- <u>Hybrid SSDs</u> are proposed

- Along with <u>System-level</u> mitigation techniques (over-provisioning, wear-leveling, read-retry, etc.)

- in Device-level: Passive and Accelerated Recovery for temporary wearout

**<u>Circadian Rhythm of Flash</u>**: preventing permanent wearout

Yoo, Sangjin, and Dongkun Shin. "Reinforcement Learning-Based {SLC} Cache Technique for Enhancing {SSD} Write Performance." 12th {USENIX} Workshop on Hot Topics in Storage and File Systems (HotStorage 20). 2020.

Circadian Rhythm of Flash

#### **Circadian Rhythm of Human**

• Sleep during the day not only at weekends

<u>Circadian Rhythm for BTI and EM wearout\*</u> <u>Circadian Rhythm of Flash</u>

\*Guo, Xinfei, and Mircea R. Stan. "Deep Healing: Ease the BTI and EM Wearout Crisis by Activating Recovery." 2017 47th Annual IEEE/IFIP International Conference on Dependable Systems and Networks Workshop (DSN-W). IEEE, 2017.

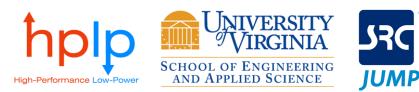

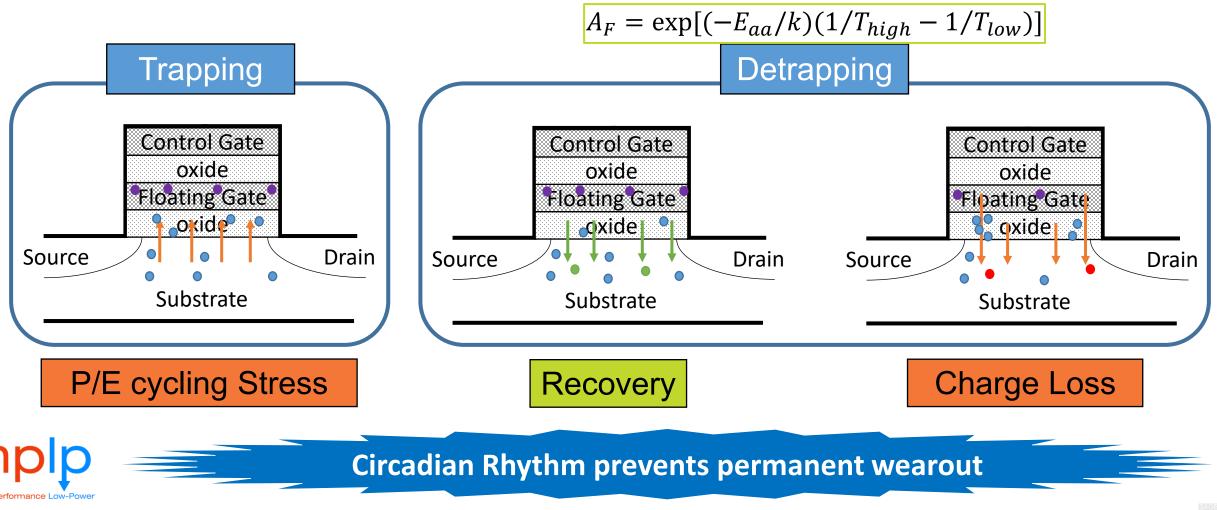

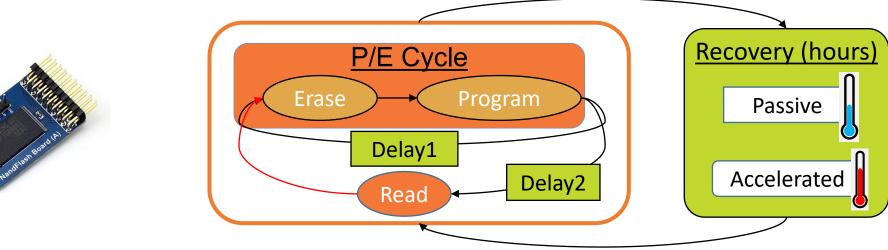

#### Use (Stress) and Recovery Mechanisms

4

- Electrons are forcibly moved during Programmed and Erase operations

- <u>Recovery (detrapping)</u> efficient for temporary traps.

## Experimental Setup of Circadian Rhythms

- 21nm SLC NAND flash floating gate transistor

- no-ECC during experiments and no read-retry

- 20 P/E Cycles + 1 Read

- temperature: 95 °C

- 7 different rhythms

ECC-1: 1 bit / (512+16 Byte) ECC-4: 4 bit / (512+16 Byte)  $t_{delay1} = 1.5$  s (dwell time)  $t_{delay2} = 3$  s (retention time)

M. C. Morgul, M. N. Sakib and M. Stan, **Reliable Processing in Flash with High Temperature.** The IEEE International Integrated Reliability Workshop (IIRW) 2021, October 4-29, 2021 https://www.waveshare.com/nandflash-board-a.htm

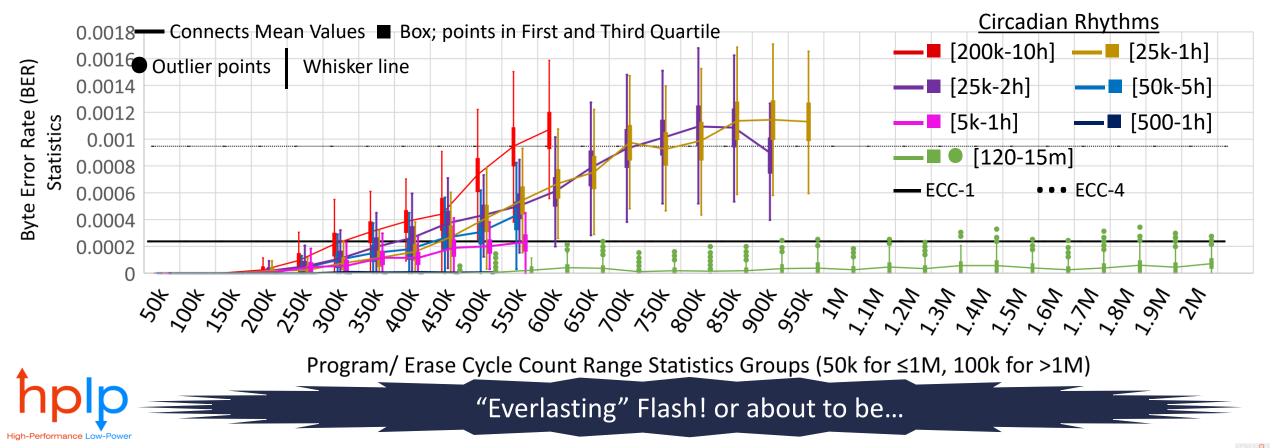

Circadian Rhythm on Prevention of Permanent Wearout

- The rhythm of [120-15m] (i.e., 120 P/E cycles followed by 15 min of recovery) , compared to [200k-10h].

- increases lifetime with ECC-1 2.9x; but only 60 times exceed ECC-1 till 1.95M, which actually means 9x improvement

- <u>decreases</u> the slope of linear fit <u>by 70x</u> flattens the trend

Circadian Rhythm on Prevention of Permanent Wearout

• The rhythm of [120-15m], compared to [200k-10h].

High-Performance Low-Poy

increases lifetime with ECC-1 2.9x; but only 60 times exceed ECC-1 till 1.95M, which actually means 9x improvement

| Circadian Rhythm                  | BER = ECC-1         | BER = ECC-1 Lifetime Improvement |         | Slope in Linear Fit |  |  |

|-----------------------------------|---------------------|----------------------------------|---------|---------------------|--|--|

| 200k-10h                          | 223k                | baseline                         | 1.2e-9  | 1x                  |  |  |

| 25k-1h                            | 245k                | 9.8%                             | 1.6e-9  | 1.27x               |  |  |

| 25k-2h                            | 230k                | 3.1%                             | 1.6e-9  | 1.27x               |  |  |

| 50k-5h                            | 264k                | 18.3%                            | 8.5e-10 | 2.34x               |  |  |

| 5k-1h                             | 294k                | 31.8%                            | 5.1e-10 | 3.89x               |  |  |

| 500-1h                            | w.r.t. values @482k | 285.6%                           | 2.2e-11 | 90.45x              |  |  |

| 120-15m                           | 858k                | 284.7%                           | 2.7e-11 | 73.70x              |  |  |

| This is translated into <b>9x</b> |                     |                                  |         |                     |  |  |

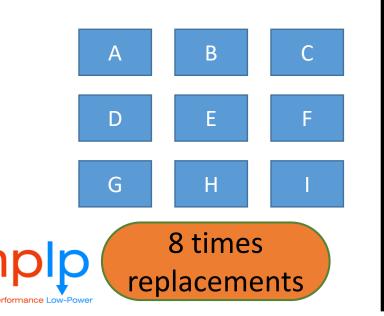

### Worst Case: High Utilization Demanding Application

- An application that requires to access all the bits (capacity) at any time

- Tremendous amount of parallelism: as high as number of bits

- Example: Processing in-memory

- With just <u>4x (5-1) more capacity</u>, <u>8x (9-1) more lifetime</u> is gained [120-15m]

- Overall more than <u>2x sustainability improvement</u> when you consider total cost of ownership

| 0                                | Time:              | 3.75m | 3.75m | 3.75m | 3.75m | 3.75m |

|----------------------------------|--------------------|-------|-------|-------|-------|-------|

| 1                                | Block <sub>0</sub> | Use   | Recov | Recov | Recov | Recov |

|                                  | Block <sub>1</sub> | Recov | Use   | Recov | Recov | Recov |

| 2                                | Block <sub>2</sub> | Recov | Recov | Use   | Recov | Recov |

| 3                                | Block <sub>3</sub> | Recov | Recov | Recov | Use   | Recov |

| 4                                | Block <sub>4</sub> | Recov | Recov | Recov | Recov | Use   |

| 9x lifetime but 4x more capacity |                    |       |       |       |       |       |

## Summary

- Existing recovery methods at **the device-level** left the **irreversible** component of wearout **uncheck**

- Circadian Rhythm prevents the occurrence of most of the permanent wearouts

- Experimental results of SLC floating gate shows that **[120-15m] Circadian Rhythm** increases lifetime of flash memory by **9x**

- Circadian Rhythm improves **sustainability** at least **2x** even in the hypothetical worst-case

### Discussion and Future Work

- Circadian Rhythm is the key to unlock "everlasting" flash memories

- Study\* shows Circadian Rhythm (CR) is up to **100% beneficial** for **Bias Temperature Instability** wearout of FETs and **ElectromMigration**

- Therefore, Circadian Rhythm recovery approach can be generalized to all electronics

- Such as to other non-volatile memories; ReRAM, FeRAM, memristors etc.

#### Future works:

- Repeating experiments for other flash technologies (i.e. charge-trap, MLC/TLC/QLC, 3D etc.)

- Augmenting FTL (Flash Transition Layer) that exploits CR

- Developing al-in-one approach that synchronizes CR for a complete system

\*Guo, Xinfei, and Mircea R. Stan. "Deep Healing: Ease the BTI and EM Wearout Crisis by Activating Recovery." 2017 47th Annual IEEE/IFIP International Conference on Dependable Systems and Networks Workshop (DSN-W). IEEE, 2017.

# Circadian Rhythm: A Candidate for Achieving Everlasting Flash Memories

\*M. Ceylan Morgul, ^Xinfei Guo and \*Mircea Stan

\*University of Virginia, Charlottesville, VA, USA

^University of Michigan – Shanghai Jiao Tong University Joint Institute, Shanghai, China

{ceylan, mircea}@virginia.edu; xinfei.guo@sjtu.edu.cn

This work was supported in part by Semiconductor Research Corporation (SRC) under

the Center for Research on Intelligent Storage and Processing in-memory (CRISP)