1

# A Joint Sneak Path and Data Detection Scheme for Resistive Random Access Memories

Guanghui Song\*, Kui Cai<sup>†</sup>, Xingwei Zhong<sup>†</sup>, and Ying Li\*

\*Xidian University, Xi'an, China

<sup>†</sup>Singapore University of Technology and Design, Singapore

### I. Introduction

Although the crossbar array structure of resistive randomaccess memory (ReRAM) brings many advantages, such as high data storage density and parallel reading/writing ability, it also causes a severe problem known as the "sneak path (SP)" interference [1]. The SP interference not only degrades the data detection accuracy but also leads to strong inter-cell correlation. A cell selector is usually introduced in series to each memory cell to avoid the SPs. However, in practice, it is also prone to failures due to the imperfection of the memory fabrication and maintenance process, leading to the re-occurrence of SPs [1], [2]. By modeling the selector failure (SF) as a random event, several data detection schemes have been proposed by Ben-Hur et al. [1] and Chen et al. [2] based on communication and coding theories. However, all these schemes are suboptimal since none of the schemes have fully utilized the inter-cell correlation during data detection, and the SP interference is in general treated as independent noise.

In this work, we propose a novel detection scheme which can jointly recover the SP interference and the input user data through fully utilizing the inter-cell correlation. Our proposed joint detection scheme can approach the performance bound of the optimal detection scheme with only linear operation complexity. It consists of the following two steps.

**Step 1**: Locations of SFs in the memory array are first detected. Data belongs to SF-located rows and columns, named as SF data, is subsequently detected by regarding the remaining data in the array as random variables.

**Step 2:** With the SF locations and the detected SF data as *a priori* information, both of the SP interference and the remaining data are detected.

We remark that the larger the memory array, the more accurate the Step 1 detection, and thereby the better the overall bit error rate (BER) performance.

## II. SNEAK-PATH MODEL

For the single-level cell ReRAM, a memory cell has two states, the high resistance state (HRS) with resistance  $R_0$  and the low resistance state (LRS) with resistance  $R_1$ , which can represent input user data bits of "0" and "1", respectively. An  $N \times N$  ReRAM array is formed by arranging  $N^2$  such memory

This work was support by RIE2020 Advanced Manufacturing and Engineering (AME) programmatic grant A18A6b0057 and Singapore Ministry of Education Academic Research Fund Tier 2 MOE2019-T2-2-123. The full journal version is published at [3].

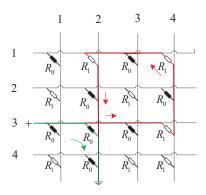

Fig. 1. Example of an SP during the reading of cell (3,2) in a  $4 \times 4$  memory array. The green line is the desired path for resistance measuring.  $(3,2) \rightarrow (3,4) \rightarrow (1,4) \rightarrow (1,2) \rightarrow (3,2)$  forms an SP (red line) in parallel to target cell (3,2) that degrades the measured resistance value. Note that the horizontal and vertical lines are connected via intersectional memory cells. Arrows show current flow directions. A reverse current flows across cell (1,4).

cells in a crossbar structure, and therefore, it can store an  $N \times N$  bit array. To recover the stored bit array from an ReRAM array, the resistance state of each memory cell in the array should be detected. Specifically, to detect cell (m, n), a voltage is applied to the m-th row and n-th column of the ReRAM array and a current goes through cell (m, n). If the cell is detected as HRS, the corresponding bit is identified as a "0", and if it is detected as LRS, the bit is identified as a "1". The major challenge of this process is the existence of SP in the ReRAM array, which produces current interference to the data detection. Following the simplified SP model proposed by Chen et al. [2], an SP is defined as a path that originates from and returns to a cell while traversing 3 LRS cells through alternating vertical and horizontal steps.

Fig. 1 shows an example of a SP that is formed during the reading of cell (3, 2). A direct impact of the SP is a reduction of the readback resistance. Thus, the detected resistance value in this case becomes

$$R_0' = \left(\frac{1}{R_0} + \frac{1}{R_c}\right)^{-1} < R_0 \tag{1}$$

where  $R_s$  is the parasitic resistance value introduced by the SP. Note that SPs actually benefit the data detection when the target cell is in LRS. They are detrimental only when an HRS cell is read, making it more vulnerable to noise. For this reason, we only consider SPs when an HRS cell is read.

Following the work of Chen *et al.* [2], we consider 1D1R ReRAM arrays with random SFs. Assume  $X = [x_{m,n}]_{N \times N}$  is

the bit array stored in the ReRAM array, where  $x_{m,n} \in \{0, 1\}$  is stored in cell (m, n). Cell (m, n) is affected by the SP interference if the following conditions are satisfied:

- 1)  $x_{m,n} = 0$ .

- 2)  $x_{m,j} = x_{i,j} = x_{i,n} = 1$  holds for some  $i, j \in \{1, ..., N\}$ .

- 3) The selector at diagonal cell (i, j) fails.

Let  $e_{m,n}$  be an SP indicator, i.e.,  $e_{m,n} = 1$  if cell (m, n) is affected by the SP interference, and  $e_{m,n} = 0$  otherwise. The readback signal array  $\mathbf{Y} = [y_{m,n}]_{N \times N}$  is given by:

$$y_{m,n} = r_{m,n} + \eta_{m,n} \tag{2}$$

with

$$r_{m,n} = \begin{cases} \left( \left( \frac{1}{R_0} + \frac{e_{m,n}}{R_s} \right)^{-1} & \text{if } x_{m,n} = 0 \\ R_1 & \text{if } x_{m,n} = 1 \end{cases}$$

(3)

where  $\eta_{m,n} \sim \mathcal{N}(0, \sigma^2), m = 1, ..., N, n = 1, ..., N$ , is an additive Gaussian noise with mean 0 and variance  $\sigma^2$  [1].

#### III. JOINT SP AND DATA DETECTION SCHEME

The fundamental problem of ReRAM data detection is to recover stored data array X based on readback signal array Y in the presence of SP interference  $[e_{m,n}]_{N\times N}$  and Gaussian noise  $[\eta_{m,n}]_{N\times N}$ .

We first reformulate the readback signal. Let

$$\varphi_{sf} = \left\{ (i, j) | x_{i,j} = 1, \text{ selector fails at } (i, j) \right\}$$

$$R_x(e) = \left( \frac{1}{R_x} + (1 - x) \frac{e}{R_s} \right)^{-1}, \text{ for } x, e \in \{0, 1\}.$$

Based on the SP occurrence condition, the readback resistance in (2) can be rewritten as

$$r_{m,n} = R_{x_{m,n}}(e_{m,n}) = R_{x_{m,n}}\left(\bigcup_{(i,j)\in\{0,s\}} x_{i,n}x_{m,j}\right)$$

(4)

where  $\bigcup$  is the logical OR operator, i.e.,  $\bigcup_{(i,j)\in\varphi_{sf}} x_{i,n}x_{m,j} = 1$  if at least one of  $(i,j)\in\varphi_{sf}$  with  $x_{i,n}x_{m,j} = 1$  exists, otherwise,  $\bigcup_{(i,j)\in\varphi_{sf}} x_{i,n}x_{m,j} = 0$ . Therefore,  $r_{m,n}$  is a function of  $x_{m,n}$ , the SF locations, and the SF data.

Due to cell correlation caused by SP interference, a coarse maximum likelihood (ML) detection,  $X = \arg\max_{X} \Pr(Y|X|)$ , requires immense computation complexity. However, we noticed that from (4) once the SF locations,  $\varphi_{sf}$ , and the SF data,  $X_{sf}: x_{i,n}, x_{m,j}, (i,j) \in \varphi_{sf}, m=1,...,N, n=1,...,N$ , are known, the SP indicator  $[e_{m,n}]_{N\times N}$  will be recovered, and the remaining data can be detected independently based on a bitwise ML rule. Therefore, we propose the following two-step joint SP and data detection scheme.

Step 1:

$$(\hat{\varphi}_{sf}, \hat{X}_{sf}) = \arg \max_{\varphi_{sf}, \hat{X}_{sf}} \Pr(Y|\varphi_{sf}, X_{sf})$$

Recover SP  $\hat{e}_{m,n} = \bigcup_{(i,j) \in \hat{\varphi}_{sf}} \hat{x}_{i,n} \hat{x}_{m,j}$ .

**Step 2:**

$$\hat{x}_{m,n} = \arg\min_{d=0,1} |y_{m,n} - R_d(\hat{e}_{m,n})|, (m,n) \notin \varphi_{sf}.$$

Note that **Step 2** is a bit-wise ML detection over Gaussian noisy channel. To carry out **Step 1**, we need to reveal some properties of SP. These properties as well as the detail computations of **Step 1** can be found in the journal version of this abstract [3].

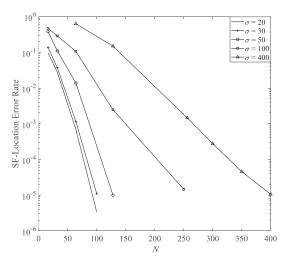

Fig. 2. Detection error rate of SF locations when the number of SFs in the array is less than 3, with  $R_0 = 1000\Omega$ ,  $R_1 = 100\Omega$ , and  $R_s = 250\Omega$ .

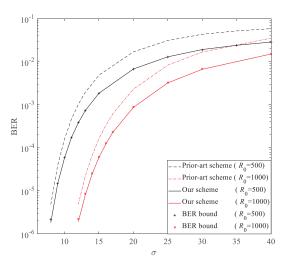

Fig. 3. Data detection BER with N=128 and i.i.d SFs with  $p_f=10^{-4}$  (for  $R_0=500$ ) and  $p_f=2\times 10^{-4}$  (for  $R_0=1000$ ).  $R_1=100\Omega$ , and  $R_s=250\Omega$ . The BER of the prior art scheme shows the result of the detection scheme proposed by Ben-Hur and Cassuto [1] (the single-threshold scheme used in Chen *et al.* [2]).

# IV. SIMULATION RESULS

Figure 2 shows that as the array size *N* increases, the detection of the SF locations becomes very accurate. Similar results are observed for the SF data detection [3]. Figure 3 shows that our detection scheme achieves much lower BER than the prior art scheme. It can approach the BER lower bound of the optimal detection scheme derived in [3].

# REFERENCES

- Y. Ben-Hur and Y. Cassuto, "Detection and coding schemes for sneakpath interference in resistive memory arrays," *IEEE Trans. Commun.*, vol. 67, no. 6, pp. 3821–3833, Feb. 2019.

- [2] Z. Chen, C. Schoeny, and L. Dolecek, "Pilot assisted adaptive thresholding for sneak-path mitigation in resistive memories with failed selection devices," *IEEE Trans. Commun.*, vol. 68, no. 1, pp. 66–81, Jan. 2020.

- [3] G. Song, K. Cai, C. Sun, X. Zhong and J. Cheng, "Near-optimal detection for both data and sneak-path interference in resistive memories with random cell selector failures," *IEEE Trans. Commun.*, vol. 70, no. 2, pp.836–850, Feb. 2022.